# MODEL 5/16 USER'S MANUAL

PERKIN-ELMER DATA SYSTEMS 2 Crescent Place, Oceanport, N.J. 07757 • (201) 229-4040

> © INTERDATA INC., 1977 All Rights Reserved Printed in U.S.A. February 1977

# PAGE REVISION STATUS SHEET

PUBLICATION NUMBER 29-588

TITLE Model 5/16 User's Manual

REVISION ROO

19dr

DATE 4/28/77

|                              | ****         |        |                               |      |      |      |      |      |

|------------------------------|--------------|--------|-------------------------------|------|------|------|------|------|

| PAGE                         | REV.         | DATE   | PAGE                          | REV. | DATE | PAGE | REV. | DATE |

| i/ii<br>dii<br>thru          | R00<br>R00   | 4/77   | A2-1<br>thru<br>A2-3/<br>A2-4 | R00  | 4/77 |      |      |      |

| 1-1<br>thru<br>1-3/          | R00          | 4/77   | A3-1<br>thru<br>A3-3/<br>A3-4 | R00  | 4/77 |      | ·    |      |

| 2-1                          | R00          | 4/77   | A4-1,<br>A4-2                 | R00, | 4/77 |      | ,    |      |

| thru<br>2-9/<br>2-10         |              |        | A5-1<br>thru<br>A5-6          | R00  | 4/77 |      |      |      |

| 3-1<br>thru<br>3-31/         | R00          | 4/77   | A6-1,<br>A6-2                 | R00  | 4/77 |      |      |      |

| 3-32<br>4-1<br>thru          | R <b>0</b> 0 | 4/77   | A7-1<br>thru<br>A7-4          | R00  | 4/77 | P .  |      |      |

| 4-23/4-24                    | D00          | 1 /77  | A8-1,<br>A8-2                 | R00  | 4/77 |      | ·    | :    |

| 5-1<br>thru<br>5-16          | R00          | 4/77   | A9-1<br>thru<br>A9-3/         | R00  | 4/77 |      |      |      |

| 6-1<br>thru<br>6-8           | R00          | 4/77   | A9-4<br>A10-1                 |      | 4/77 |      | •    |      |

| 7-1<br>thru                  | R00          | 4/77   | thru<br>Al0-6                 |      |      |      |      |      |

| 7-21/<br>7-22                |              | .P. ni | All-1<br>thru<br>All-3        | γ .  | 4/77 |      |      |      |

| 8-1<br>thru<br>8-38          | R00          | 4/77   | All-4                         | R00  | 4/77 |      |      |      |

| 9-1<br>thru<br>A1-1/<br>A1-2 | R00          | 4/77   | thru<br>I-3/<br>I-4           |      |      |      |      |      |

# **FOREWORD**

The Model 5/16 User's Manual provides information for the programmer, designer, and operator in the use of the Model 5/16 computer system. The programmer is given a detailed description of each instruction in the Model 5/16 instruction set. Such information includes valuable system related information presented in the form of programming notes, examples, and Condition Codes. To assist the designer in choosing his own controller interface to the Model 5/16 system, a wealth of design information is presented on the Input/Output portion of the Model 5/16, corresponding to the Micro I/O and the Multiplexor Busses. ASCII Programmer's Console information is given in the manual to facilitate program preparation and execution for the programmer and operator of the system. Finally, several Appendices are included as valuable reference information for Model 5/16 users.

29-588 R00 2/77 i/ii

-.

# Table of Contents

| CHAPTER 1 INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <br>1-                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

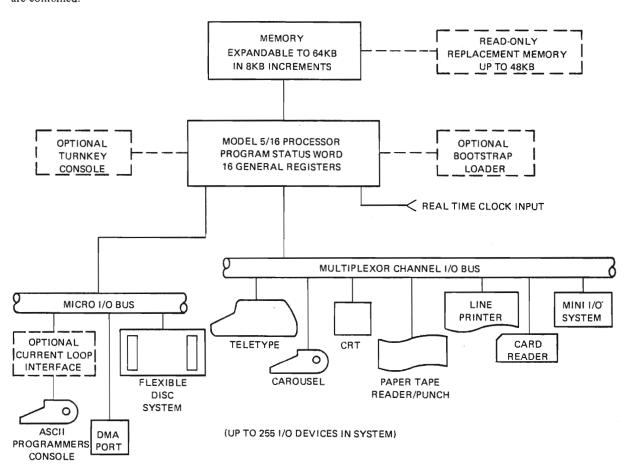

| SYSTEM ARCHITECTURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1-1                                                                                     |

| MEMORY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <br>1-1                                                                                 |

| INSTRUCTION SET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <br>1-1                                                                                 |

| INPUT/OUTPUT SYSTEM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <br>1-2                                                                                 |

| SOFTWARE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1-2                                                                                     |

| PROCESSOR OPTIONS AND PERIPHERALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1-2                                                                                     |

| CHAPTER 2 SYSTEM DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <br>2-1                                                                                 |

| PROCESSOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <br>2-1                                                                                 |

| Program Status Word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2-2                                                                                     |

| Processor Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-3                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-3                                                                                     |

| General Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2-3                                                                                     |

| Reserved Memory Locations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <br>2-3                                                                                 |

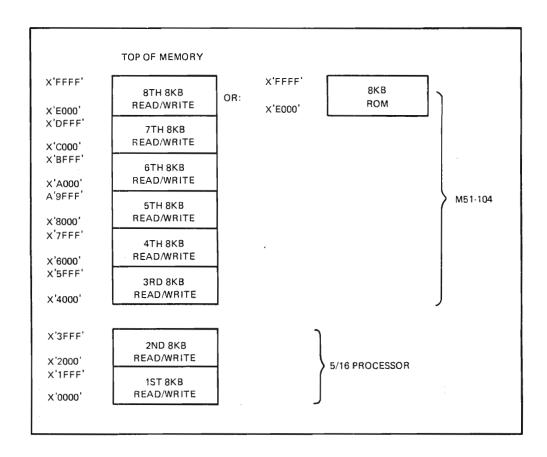

| MEMORY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2-4                                                                                     |

| Memory Expansion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-4                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-5                                                                                     |

| Memory Addressable ROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                         |

| Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2-5                                                                                     |

| PROCESSOR OPERATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <br>2-5                                                                                 |

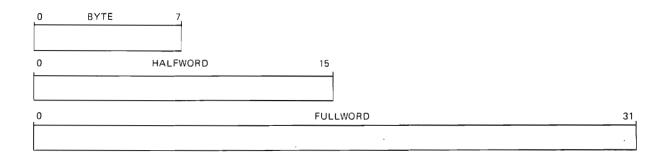

| DATA FORMATS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <br>2-6                                                                                 |

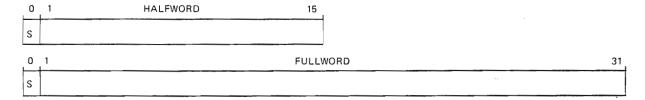

| Fixed Point Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <br>2-6                                                                                 |

| Logical Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-6                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                         |

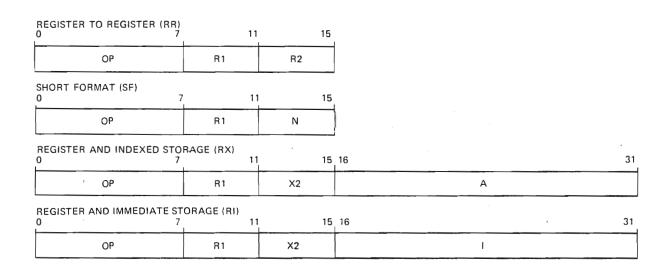

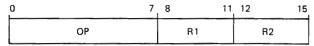

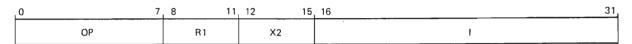

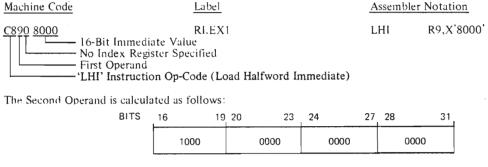

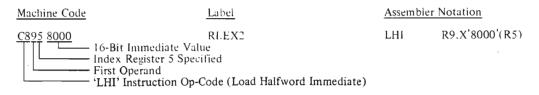

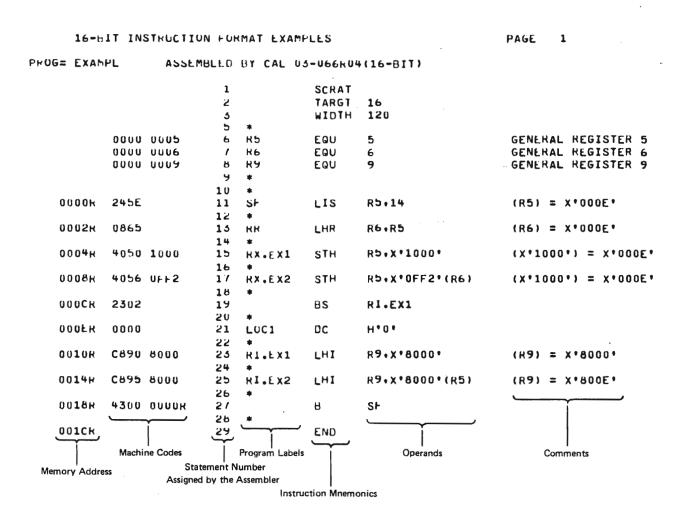

| INSTRUCTION FORMATS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2-6                                                                                     |

| Branch Instruction Formats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2-7                                                                                     |

| Programming Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <br>2-7                                                                                 |

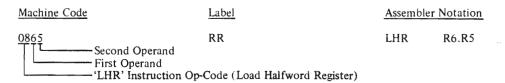

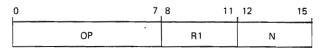

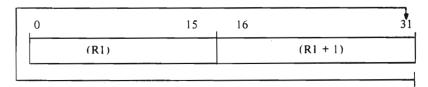

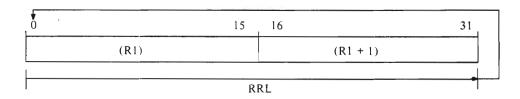

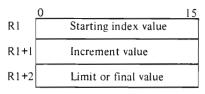

| Register to Register (RR) Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <br>2-7                                                                                 |

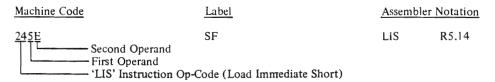

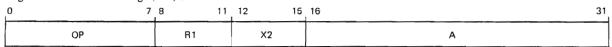

| Short Form (SF) Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <br>2-7                                                                                 |

| Desired and Indianal Change (DV) Courses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <br>2-7                                                                                 |

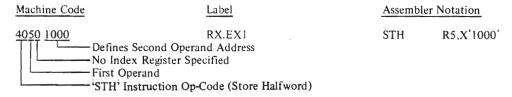

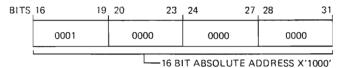

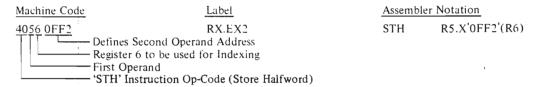

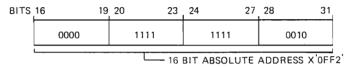

| Register and Indexed Storage (RX) Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                         |

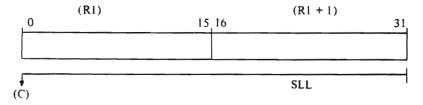

| Register and Immediate Storage (RI) Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <br>2-8                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                         |

| CHAPTER 3 LOGICAL OPERATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3-1                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                         |

| INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <br>3-1                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <br>3-1<br>3-2                                                                          |

| INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <br>3-1                                                                                 |

| INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <br>3-1<br>3-2<br>3-2                                                                   |

| INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <br>3-1<br>3-2<br>3-2<br>3-3                                                            |

| INTRODUCTION  DATA FORMATS  Boolean Operations  List Processing  LOGICAL INSTRUCTION FORMATS                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <br>3-1<br>3-2<br>3-3<br>3-3                                                            |

| INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <br>3-1<br>3-2<br>3-2<br>3-3                                                            |

| INTRODUCTION  DATA FORMATS  Boolean Operations  List Processing  LOGICAL INSTRUCTION FORMATS  LOGICAL INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <br>3-1<br>3-2<br>3-3<br>3-4<br>3-4                                                     |

| INTRODUCTION  DATA FORMATS  Boolean Operations  List Processing  LOGICAL INSTRUCTION FORMATS                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <br>3-1<br>3-2<br>3-3<br>3-3                                                            |

| INTRODUCTION  DATA FORMATS  Boolean Operations  List Processing  LOGICAL INSTRUCTION FORMATS  LOGICAL INSTRUCTIONS  CHAPTER 4 BRANCHING                                                                                                                                                                                                                                                                                                                                                                                                                            | <br>3-1<br>3-2<br>3-3<br>3-4<br>3-4                                                     |

| INTRODUCTION  DATA FORMATS  Boolean Operations  List Processing  LOGICAL INSTRUCTION FORMATS  LOGICAL INSTRUCTIONS  CHAPTER 4 BRANCHING  OPERATIONS                                                                                                                                                                                                                                                                                                                                                                                                                | <br>3-1<br>3-2<br>3-3<br>3-4<br>3-4<br>4-1<br>4-1                                       |

| INTRODUCTION  DATA FORMATS  Boolean Operations List Processing  LOGICAL INSTRUCTION FORMATS LOGICAL INSTRUCTIONS  CHAPTER 4 BRANCHING  OPERATIONS Decision Making                                                                                                                                                                                                                                                                                                                                                                                                  | 3-1<br>3-2<br>3-2<br>3-3<br>3-4<br>4-1<br>4-1<br>4-1                                    |

| INTRODUCTION  DATA FORMATS  Boolean Operations List Processing  LOGICAL INSTRUCTION FORMATS  LOGICAL INSTRUCTIONS  CHAPTER 4 BRANCHING  OPERATIONS  Decision Making Subroutine Linkage                                                                                                                                                                                                                                                                                                                                                                             | 3-1<br>3-2<br>3-3<br>3-4<br>3-4<br>4-1<br>4-1<br>4-1<br>4-1                             |

| INTRODUCTION  DATA FORMATS  Boolean Operations List Processing  LOGICAL INSTRUCTION FORMATS  LOGICAL INSTRUCTIONS  CHAPTER 4 BRANCHING  OPERATIONS  Decision Making Subroutine Linkage  BRANCH INSTRUCTION FORMATS                                                                                                                                                                                                                                                                                                                                                 | 3-1<br>3-2<br>3-3<br>3-4<br>3-4<br>4-1<br>4-1<br>4-1<br>4-1                             |

| INTRODUCTION  DATA FORMATS  Boolean Operations List Processing  LOGICAL INSTRUCTION FORMATS  LOGICAL INSTRUCTIONS  CHAPTER 4 BRANCHING  OPERATIONS  Decision Making Subroutine Linkage  BRANCH INSTRUCTIONS  BRANCH INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                   | 3-1<br>3-2<br>3-3<br>3-4<br>4-1<br>4-1<br>4-1<br>4-1<br>4-1                             |

| INTRODUCTION  DATA FORMATS  Boolean Operations List Processing  LOGICAL INSTRUCTION FORMATS  LOGICAL INSTRUCTIONS  CHAPTER 4 BRANCHING  OPERATIONS  Decision Making Subroutine Linkage  BRANCH INSTRUCTIONS  BRANCH INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                   | 3-1<br>3-2<br>3-3<br>3-4<br>3-4<br>4-1<br>4-1<br>4-1<br>4-1                             |

| INTRODUCTION  DATA FORMATS  Boolean Operations List Processing  LOGICAL INSTRUCTION FORMATS  LOGICAL INSTRUCTIONS  CHAPTER 4 BRANCHING  OPERATIONS  Decision Making Subroutine Linkage  BRANCH INSTRUCTIONS  BRANCH INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                   | 3-1<br>3-2<br>3-3<br>3-4<br>4-1<br>4-1<br>4-1<br>4-1<br>4-1                             |

| INTRODUCTION DATA FORMATS  Boolean Operations List Processing LOGICAL INSTRUCTION FORMATS LOGICAL INSTRUCTIONS  CHAPTER 4 BRANCHING  OPERATIONS Decision Making Subroutine Linkage BRANCH INSTRUCTION FORMATS BRANCH INSTRUCTIONS  EXTENDED BRANCH MNEMONICS                                                                                                                                                                                                                                                                                                       | 3-1<br>3-2<br>3-3<br>3-4<br>4-1<br>4-1<br>4-1<br>4-1<br>4-1                             |

| INTRODUCTION DATA FORMATS  Boolean Operations List Processing  LOGICAL INSTRUCTION FORMATS LOGICAL INSTRUCTIONS  CHAPTER 4 BRANCHING  OPERATIONS Decision Making Subroutine Linkage BRANCH INSTRUCTION FORMATS BRANCH INSTRUCTION FORMATS BRANCH INSTRUCTIONS  EXTENDED BRANCH MNEMONICS  CHAPTER 5 FIXED POINT ARITHMETIC                                                                                                                                                                                                                                         | 3-1<br>3-2<br>3-3<br>3-4<br>4-1<br>4-1<br>4-1<br>4-1<br>5-1                             |

| INTRODUCTION DATA FORMATS Boolean Operations List Processing LOGICAL INSTRUCTION FORMATS LOGICAL INSTRUCTIONS  CHAPTER 4 BRANCHING  OPERATIONS Decision Making Subroutine Linkage BRANCH INSTRUCTION FORMATS BRANCH INSTRUCTION FORMATS BRANCH INSTRUCTIONS EXTENDED BRANCH MNEMONICS  CHAPTER 5 FIXED POINT ARITHMETIC  DATA FORMATS                                                                                                                                                                                                                              | 3-1<br>3-2<br>3-3<br>3-4<br>4-1<br>4-1<br>4-1<br>4-1<br>5-1<br>5-1                      |

| INTRODUCTION DATA FORMATS Boolean Operations List Processing LOGICAL INSTRUCTION FORMATS LOGICAL INSTRUCTIONS  CHAPTER 4 BRANCHING  OPERATIONS Decision Making Subroutine Linkage BRANCH INSTRUCTION FORMATS BRANCH INSTRUCTIONS EXTENDED BRANCH MNEMONICS  CHAPTER 5 FIXED POINT ARITHMETIC  DATA FORMATS FIXED POINT NUMBER RANGE                                                                                                                                                                                                                                | 3-1<br>3-2<br>3-2<br>3-3<br>3-4<br>4-1<br>4-1<br>4-1<br>5-1<br>5-5                      |

| INTRODUCTION DATA FORMATS Boolean Operations List Processing LOGICAL INSTRUCTION FORMATS LOGICAL INSTRUCTIONS  CHAPTER 4 BRANCHING  OPERATIONS Decision Making Subroutine Linkage BRANCH INSTRUCTION FORMATS BRANCH INSTRUCTIONS EXTENDED BRANCH MNEMONICS  CHAPTER 5 FIXED POINT ARITHMETIC  DATA FORMATS FIXED POINT NUMBER RANGE                                                                                                                                                                                                                                | 3-1<br>3-2<br>3-2<br>3-3<br>3-4<br>4-1<br>4-1<br>4-1<br>5-5<br>5-5-5-7                  |

| INTRODUCTION DATA FORMATS Boolean Operations List Processing LOGICAL INSTRUCTION FORMATS LOGICAL INSTRUCTIONS  CHAPTER 4 BRANCHING  OPERATIONS Decision Making Subroutine Linkage BRANCH INSTRUCTION FORMATS BRANCH INSTRUCTION FORMATS BRANCH INSTRUCTIONS EXTENDED BRANCH MNEMONICS  CHAPTER 5 FIXED POINT ARITHMETIC  DATA FORMATS FIXED POINT NUMBER RANGE FIXED POINT INSTRUCTION FORMATS                                                                                                                                                                     | 3-1<br>3-2<br>3-2<br>3-3<br>3-4<br>4-1<br>4-1<br>4-1<br>5-5<br>5-5-5-7                  |

| INTRODUCTION DATA FORMATS Boolean Operations List Processing LOGICAL INSTRUCTION FORMATS LOGICAL INSTRUCTIONS  CHAPTER 4 BRANCHING  OPERATIONS Decision Making Subroutine Linkage BRANCH INSTRUCTION FORMATS BRANCH INSTRUCTION FORMATS BRANCH INSTRUCTIONS EXTENDED BRANCH MNEMONICS  CHAPTER 5 FIXED POINT ARITHMETIC  DATA FORMATS FIXED POINT NUMBER RANGE FIXED POINT INSTRUCTION FORMATS                                                                                                                                                                     | 3-1<br>3-2<br>3-2<br>3-3<br>3-4<br>4-1<br>4-1<br>4-1<br>5-1<br>5-5                      |

| INTRODUCTION DATA FORMATS Boolean Operations List Processing LOGICAL INSTRUCTION FORMATS LOGICAL INSTRUCTIONS  CHAPTER 4 BRANCHING  OPERATIONS Decision Making Subroutine Linkage BRANCH INSTRUCTION FORMATS BRANCH INSTRUCTIONS EXTENDED BRANCH MNEMONICS  CHAPTER 5 FIXED POINT ARITHMETIC  DATA FORMATS FIXED POINT NUMBER RANGE FIXED POINT INSTRUCTION FORMATS FIXED POINT INSTRUCTION FORMATS FIXED POINT INSTRUCTION FORMATS FIXED POINT INSTRUCTION FORMATS FIXED POINT INSTRUCTIONS                                                                       | 3-1<br>3-2<br>3-2<br>3-3<br>3-4<br>4-1<br>4-1<br>4-1<br>5-5<br>5-5-5-7                  |

| INTRODUCTION DATA FORMATS Boolean Operations List Processing LOGICAL INSTRUCTION FORMATS LOGICAL INSTRUCTIONS  CHAPTER 4 BRANCHING  OPERATIONS Decision Making Subroutine Linkage BRANCH INSTRUCTION FORMATS BRANCH INSTRUCTION FORMATS BRANCH INSTRUCTIONS EXTENDED BRANCH MNEMONICS  CHAPTER 5 FIXED POINT ARITHMETIC  DATA FORMATS FIXED POINT NUMBER RANGE FIXED POINT INSTRUCTION FORMATS FIXED POINT INSTRUCTION FORMATS FIXED POINT INSTRUCTION FORMATS FIXED POINT INSTRUCTION FORMATS FIXED POINT INSTRUCTIONS  CHAPTER 6 STATUS SWITCHING AND INTERRUPTS | 3-1<br>3-2<br>3-3<br>3-4<br>4-1<br>4-1<br>4-1<br>5-5-5-5-5-5-5-7                        |

| INTRODUCTION DATA FORMATS Boolean Operations List Processing LOGICAL INSTRUCTION FORMATS LOGICAL INSTRUCTIONS CHAPTER 4 BRANCHING  OPERATIONS Decision Making Subroutine Linkage BRANCH INSTRUCTION FORMATS BRANCH INSTRUCTION FORMATS BRANCH INSTRUCTIONS EXTENDED BRANCH MNEMONICS CHAPTER 5 FIXED POINT ARITHMETIC DATA FORMATS FIXED POINT NUMBER RANGE FIXED POINT INSTRUCTIONS FIXED POINT INSTRUCTIONS FIXED POINT INSTRUCTION FORMATS FIXED POINT INSTRUCTION FORMATS FIXED POINT INSTRUCTIONS CHAPTER 6 STATUS SWITCHING AND INTERRUPTS INTRODUCTION      | 3-1<br>3-2<br>3-3<br>3-4<br>4-1<br>4-1<br>4-1<br>5-5<br>5-5<br>5-6                      |

| INTRODUCTION DATA FORMATS Boolean Operations List Processing LOGICAL INSTRUCTION FORMATS LOGICAL INSTRUCTIONS  CHAPTER 4 BRANCHING  OPERATIONS Decision Making Subroutine Linkage BRANCH INSTRUCTION FORMATS BRANCH INSTRUCTION FORMATS BRANCH INSTRUCTIONS EXTENDED BRANCH MNEMONICS  CHAPTER 5 FIXED POINT ARITHMETIC  DATA FORMATS FIXED POINT NUMBER RANGE FIXED POINT INSTRUCTION FORMATS FIXED POINT INSTRUCTION FORMATS FIXED POINT INSTRUCTION FORMATS FIXED POINT INSTRUCTION FORMATS FIXED POINT INSTRUCTIONS  CHAPTER 6 STATUS SWITCHING AND INTERRUPTS | 3-1<br>3-2<br>3-2<br>3-3<br>3-4<br>4-1<br>4-1<br>4-1<br>5-1<br>5-1<br>5-1<br>5-1<br>5-1 |

# Table of Contents (Continued)

| INTERRU   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6-2          |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

|           | external Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6-3          |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6-3          |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6-3<br>6-4   |

|           | llegal Instruction Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6-4          |

|           | Supervisor Call Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6-4          |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6-4          |

| STATUS    | WITCHING INSTRUCTION FORMATS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6-4          |

| STATUS    | WITCHING INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6-4          |

| СНАРТЕ    | 7 INPUT/OUTPUT OPERATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7-1          |

| DEVICE    | ON ROLLENG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7-1          |

|           | Device Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7-1<br>7-2   |

|           | Processor/Controller Communication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7-2<br>7-2   |

| INTERRI   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7-2          |

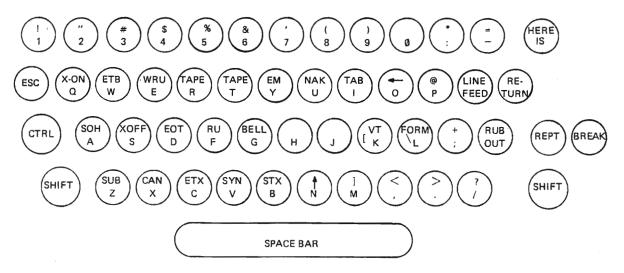

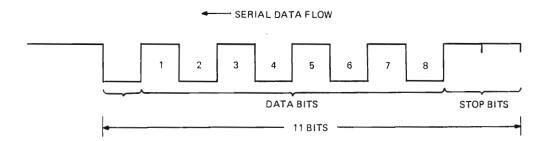

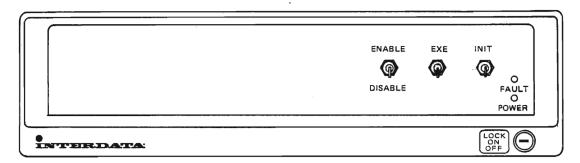

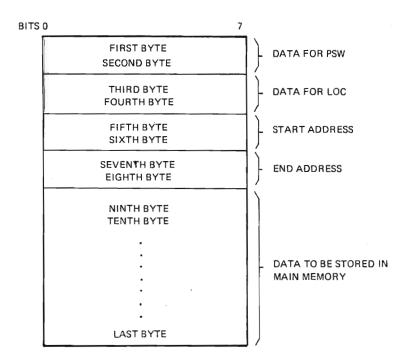

| I/O INST  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7-3          |